Vhdl Program 4 Bit Shift Register

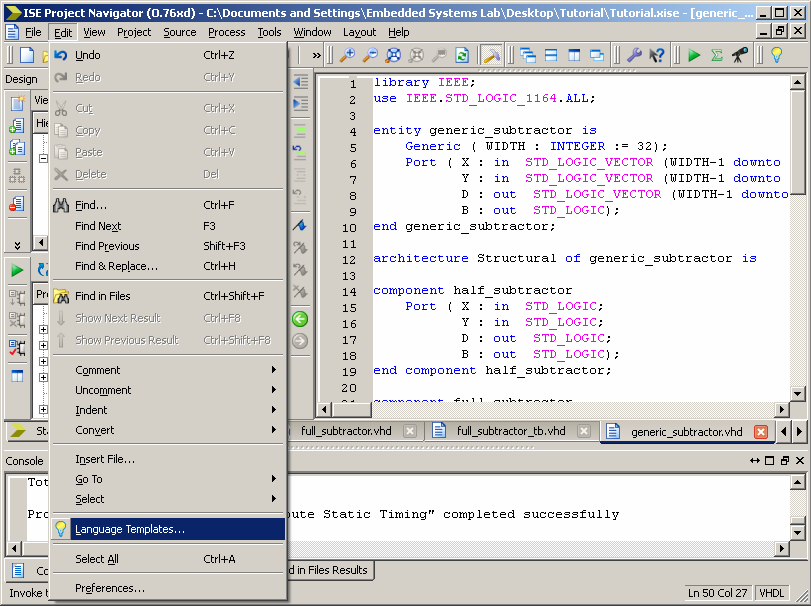

I'm trying to make a VHDL code for 4-bit universal shift register, where I want to load 4 bits and choose the shift-operation from the ctrl. I don't know how to implement a clock divider to run the outputs on a FPGA. Here is my code so far: library IEEE; use IEEE.STD_LOGIC_1164.all; entity shift_register is generic(N: integer:= 4); port( clk, reset: in std_logic; ctrl: in std_logic_vector(1 downto 0); d: in std_logic_vector((N-1) downto 0); q: out std_logic_vector((N-1) downto 0) ); end shift_register; architecture Behavioral of shift_register is signal r_reg: std_logic_vector((N-1) downto 0); signal r_next: std_logic_vector((N-1) downto 0); begin process(clk, reset) begin if(reset = '1') then r_reg '0'); elsif(clk'event and clk = '1') then r_reg. Divider code template with enable asserted a single cycle every RATIO clock cycles: library ieee; use ieee.numeric_std.all; architecture syn of mdl is constant RATIO: natural:= 10; signal prescale: std_logic_vector(9 downto 0); -- Scale to fit RATIO - 1 signal enable: std_logic; begin process (clk, reset) is begin if reset = '1' then enable.

• Shift Register Concepts • VHDL Implementation • Synthesis Considerations • Typical Uses For a Verilog shift register, see our with example code and Verilog specific tips. Shift Register Concepts A shift register is a series of connected registers (flip-flops) that are sequentially connected together so that a value at the input is passed from one register to the next on each clock cycle. In some designs, every register element can be accessed individually, while other implementations only allow access at specific locations. An illustration of a shift register is shown below, where data is entering the register chain at the least significant bit (LSB), or the right side of the picture. The above illustration shows a single-bit wide shift register with a length of 8, but there is nothing special about those numbers. Depending on the implementation method (code or IP), any practical dimensions can be used.

A single-bit shift register can be implemented in VHDL using the std_logic_vector construct. If you want to shift multiple bits at a time (e.g. A byte, word, double word, etc.), the shift register must use a custom type defined by you. Le Petit Robert 2010 Windows Crack Key.

The custom type needed to form the multi-bit width shift register is simply an array of the std_logic_vector construct. An 8-bit wide shift register that is 32 bytes in length uses this custom signal type: [cc lang=”vhdl” noborder=”true” tab_size=”4″ lines=”-1″ width=”600″ escaped=”true”] type sr32x8 is array (0 to 31) of std_logic_vector(7 downto 0); signal shift_reg: sr32x8; construct. [/cc] The code example implements both a single- and multi-bit shift register.

Typical Uses Shift registers are used whenever you’d like to delay the data signal by one or more clock cycles so that you can use it later–either for a data operation or output. One common example would be to equalize the delay of two parallel signals–possibly a data and a data valid indicator. Often a data valid indicator is delayed to match the latency of operations performed on the data stream. Happy coding! We want to hear from you! Do you have a comment, question, or suggestion? Feel free to drop us an email or post a comment.

I'm trying to make a VHDL code for 4-bit universal shift register, where I want to load 4 bits and choose the shift-operation from the ctrl. I don't know how to. But when I used to program in VHDL. A std_logic_vector of 24 bit dato_cu is a std_logic_vector of 32 bit. Spybot Full Version. Shift left register using VHDL shift. VHDL 16 bit Shift Register Search and download VHDL 16 bit Shift Register open source project / source codes from CodeForge.com.